ハードウェアを巻き込んだソフトウェア開発

ハードウェアには馴染みが薄いソフトウェア技術者も多いと思います。しかしながら、FPGA(Field-Programmable Gate Array)やGPU(Graphics Processing Unit)といったハードウェアは、人工知能(AI)を実現するためのシステムや、ビッグデータを取り扱うシステムで使われています。また、ArduinoやRaspberry Piといった安価なボードコンピュータを利用することでIoT(Internet Of Things)デバイスを簡単に利用/開発できるようになってきています。今やソフトウェア技術者にとってもハードウェアに触れる機会は増えてきています。

さまざまなシステムでハードウェアが導入される一方で、システムはますます複雑になっています。たくさんのデバイスやサーバが組み込まれたシステムにおいてはハードウェアに限らず、その中のソフトウェアも相互作用しながら動作しています。例えば、AIのシステムにおいては、複数のFPGAで演算処理を並行に処理させながらその演算結果を結合するといったことも行われています。こうした複数のハードウェアやソフトウェアが並行プロセスとして動作する並行システムでは、デッドロックが起きたり、演算結果の整合性が取れなかったりする機能的な問題と、効率的な並行処理が走らずにパフォーマンスが発揮されないといった性能的な問題が発生する可能性があります。

本稿では、ハードウェアとソフトウェアの両方を設計する上で、性能的な問題を開発の上流工程で解決する手法について紹介します。本稿で紹介する手法は、筆者がトップエスイープロジェクトに参加し、修了制作で提案およびツールで実現性を検証した手法です。ハードウェアやソフトウェアを並行に動作するプロセスモデルとして時間オートマトンで抽象化することで、開発の早期段階で低コストにシステムの並行性能を検証することができます。

ハードウェアアクセラレーションとは?

システムにおいて、特定の処理に特化した専用ハードウェアを追加することでシステム全体の処理を高速化する技術を「ハードウェアアクセラレーション」と呼び、追加するハードウェアをアクセラレータと呼びます。

アクセラレータの例として、ASIC(Application Specific Integrated Circuit)やFPGA、GPU等が挙げられます。ハードウェアアクセラレーションを行うことで対象の処理をハードウェアにより高速に実行できることに加えて、CPUの処理がオフロード(軽減)されることによりシステムの並行性が向上することも高速化に大きく寄与します。

事前性能検証の重要性

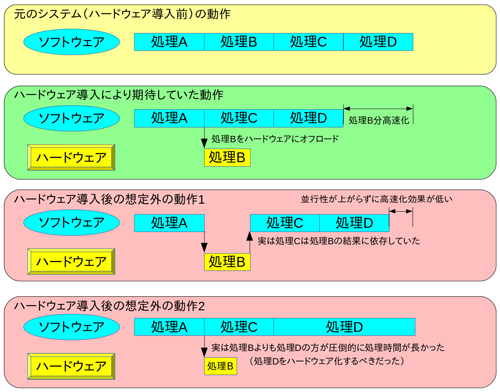

ハードウェアアクセラレーションはシステムの高速化に有効な手段のひとつですが、ハードウェアの処理中にCPUが動けず、結果的には並行性が向上しない、といったことにもつながります。また、ハードウェアに処理させる箇所以外に大きなボトルネックがあると、目的とする性能を達成できないリスクもあります。図1には、理想的なアクセラレーションに対して、2通りの想定外の動作の様子を示しました。

ハードウェアの開発にはソフトウェアと比べ、非常に大きなコストがかかるため失敗すると大きな損失になります。したがって、開発の早期段階で目的の性能要件を満たすかどうかを検証することが重要な課題となります。

ハードウェアが絡む並行システムの性能検証

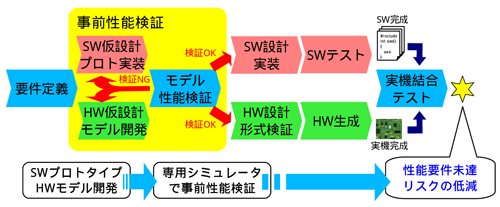

ハードウェアとソフトウェアが並行に動作する並行システムの事前検証を行う方法として、専用のシミュレータで動かしながら検証する方法が以前から利用されています(図2)。シミュレータ内で、ハードウェアは抽象化したモデルとして実現し、ソフトウェア(アプリケーションやハードウェアのドライバ等)は機能を限定したプロトタイプとして実装します。

実際にハードウェアを開発するよりは早く検証ができますが、それでもデータの入出力や多少の機能の実装が必要となることが多く、まだまだコストは小さくありません。

そこで、時間オートマトン(Timed automaton)による、機能を捨象し性能検証に特化した高抽象度のモデルで並行システムの性能検証を行う方法を紹介します。

システム検証を行うツール「UPPAAL」

(有限)オートマトンとは、有限個の状態と状態間の遷移で構成されるプロセスの動作を表現するモデルです(ここで言うプロセスとは広義の意味でのプロセスで、ソフトウェアに限らずハードウェアでも構いません)。ソフトウェア技術者に馴染み深いUMLのステートマシン図は有限オートマトンを拡張したものです。そして時間オートマトンとは、オートマトンにおける遷移や遷移条件等に時間制約の概念を追加したものになります。

この時間オートマトンでプロセスをモデル化し、複数のプロセスが並行に動作するシステムの検証を行うツールに「UPPAAL」という非常に強力なツールがあります。

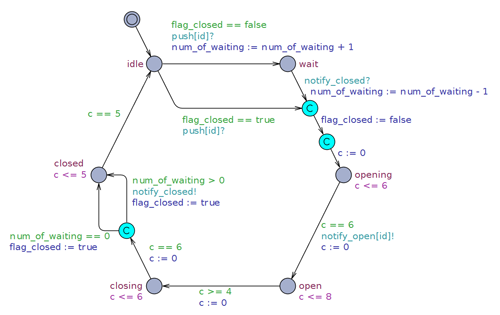

図3はUPPAALでひとつのプロセスをモデル化した一例です。

UPPAALではプロセス間のシグナルやイベントの発生タイミング、状態間の遷移タイミング等について時刻範囲でモデル化することができます。例えば、ある状態Aから状態Bに遷移するまで最悪5サイクルかかるが最速では2サイクルで済む、といった表現が可能です。このようにさまざまなタイミングについて時刻範囲でモデル化します。そして、全ての時刻範囲について網羅的に走査し、並行システム全体での性能として最悪では何サイクル、最速では何サイクルかかるかということを検証できます。

また、本稿では触れませんが、デッドロックやライブロック、変数のオーバーフローといった機能的な検証も可能です。トップエスイープロジェクトでは、オートマトンによるモデル化やモデル化したシステムを検証するさまざまな手法やツール(もちろん、UPPAALも含まれます)について学ぶ講義があります。

ソフトウェアとハードウェアのモデル化

ハードウェアアクセラレーションの効果を検証するには並行に動作するソフトウェアとハードウェアをモデル化する必要があります。

ハードウェアのモデル化はソフトウェアのモデル化に比べると単純です。なぜなら、ハードウェアは処理の開始や終了のタイミングが明確で、分岐も少なく、処理時間についてもソフトウェア程ブレがないからです。

一方で、ソフトウェアのモデル化は複雑です。特にマルチスレッドやマルチプロセスにおけるスレッドやプロセス(狭義の意味でのプロセス)、リアルタイムOSにおけるタスク等をそれぞれ異なるプロセスとして考えると、割り込みやタスク優先度の違いによるコンテキストスイッチ(プロセス間の遷移に相当)があらゆる状態で発生し得るため、これらを時間オートマトンとしてモデル化することが困難です。

また、一般的にコンテキストスイッチが発生するとレジスタを含む、メモリ空間の切り替え等のオーバーヘッドによる性能劣化につながるため、性能検証時に無視できない要素となります。

次章では、特にリアルタイムOSにおけるタスクを、時間オートマトンプロセスモデルとしてシステムの性能を検証する方法について説明します。